Averna announced that Intel has selected its DP-1000 DOCSIS Protocol Analyzer to test its DOCSIS 3.1 chipset prior to final certification.

The company said DP-1000 captures and filters MAC-layer data in real-time to verify RF parameters, validate MAC-level communication, troubleshoot interoperability issues, and improve performance, said Averna in a statement.

DP-1000 Highlights

# Supports both DOCSIS 3.0, 3.1, and some mixed mode

# Input frequency range 100 MHz–1.8 GHz DS, 5 MHz –200 MHz US

# Acquisition cards of 200 MHz bandwidth each

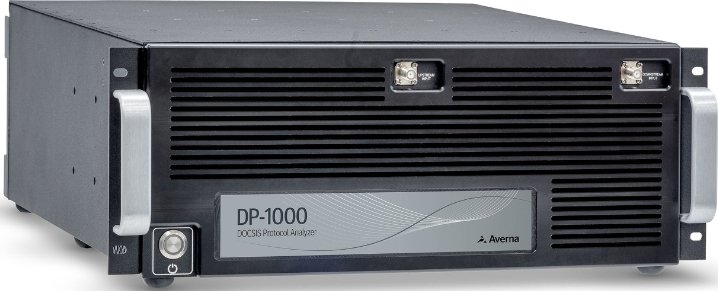

# Contained in a single, 19-inch (48 cm), 4U rack for minimal footprint (60 lbs/27 kg)

# FPGA-based architecture is highly flexible, configurable, upgradable and extendable

# Many channel-filtering, demodulation & decoding, triggering, display, and upgrade features

# Optional DOCSIS VSA enables RF spectrum and synchronized signal analysis for both US and DS, including burst, constellation, SNR, MER, EVM and power level

Averna said the DP-1000 is designed for both DOCSIS 3.0 and DOCSIS 3.1. for analyzing, debugging, maintaining and monitoring local networks and Internet connections. Averna targets multiple system operators (MSOs), chipset manufacturers, product developers and certifications bodies.

The DP-1000 analyzes up to 32×8 single or bonded US/DS channels (DOCSIS 3.0) and 2×1 OFDM US/DS channels (DOCSIS 3.1), and includes numerous channel-filtering, demodulation, triggering, display, and upgrade features.

Alex Pelland, director of Broadband Test Strategy at Averna, said: “Since DOCSIS 3.1 will enable a new generation of sophisticated products and cable services, broadband product developers like Intel will benefit from the DP-1000’s ability to accelerate the important validation and certification phases.”

editor@telecomlead.com